Pamäť s priamym prístupom (RAM) je neoddeliteľnou súčasťou mikroprocesorových systémov na rôzne účely. RAM je rozdelená do dvoch tried: statická a dynamická. V statickej RAM sú informácie uložené na spúšťačoch a v dynamickej RAM na kondenzátoroch s kapacitou asi 0,5 pF. Doba uchovávania informácií v statickej RAM nie je obmedzená, zatiaľ čo v dynamickej RAM je obmedzená časom samovybíjania kondenzátora, čo si vyžaduje špeciálne prostriedky na regeneráciu a dodatočný čas strávený týmto procesom.

Štrukturálne sa každá RAM skladá z dvoch blokov - matice úložných prvkov a dekodéra adries. Matica má z technologických dôvodov najčastejšie dvojsúradnicové dekódovanie adresy – po riadkoch a stĺpcoch. Na obr. 9.45 ukazuje maticu 16-bitovej statickej pamäte RAM. Maticu tvorí 16 pamäťových buniek mem_i, ktorých schéma je znázornená na obr. 9.46. Každá pamäťová bunka je adresovaná vstupmi X, Y výberom adresných riadkov dekodérmi pozdĺž čiar A0 ... Ax3 a stĺpcov AyO ... AyZ (pozri obr. 9.45) a dodávaním signálu logickej jednotky pozdĺž zvoleného linky. V tomto prípade sa vo vybranej pamäťovej bunke aktivuje dvojvstupový prvok AND (U1), ktorý pripraví obvody na čítanie a zápis informácií na vstupné bitové zbernice DIO ... DI3 alebo výstupné DOO ... D03. Povoľovacím signálom pre pridelenie adresy je CS (výber čipu - výber kryštálu), ktorý sa privádza na povoľovací vstup čítača adries (Addr_cnt) alebo na rovnaký vstup dekodérov pripojených k výstupom čítača.

Pri zápise do pamäťovej bunky (pozri obr. 9.46) sa na zodpovedajúcej bitovej zbernici nastaví 1 alebo 0, na vstupe WR / RD " sa nastaví signál 1 a potom, čo sú čítač alebo dekodéry adries hradlované CS signál, pracujú prvky 2I U1, U2 prvok U2 je privedený na hodinový vstup D-klopného obvodu U4, v dôsledku čoho sa do neho zapíše 1 alebo 0 v závislosti od úrovne signálu na jeho D-vstupe. .

Pri čítaní z pamäťovej bunky sa na vstupe WR / RD nastaví 0, pričom sa spustia prvky U1, U3, U5 a na vstup OUTPUT ENABLE vyrovnávacieho prvku U6 sa vyšle povoľovací signál, v dôsledku čoho signál z Q-výstupu D-klopného obvodu sa prenáša na bitovú zbernicu DOO...D03 Na testovanie fungovania pamäťovej bunky slúži generátor slov (obr. 9.47).

Moderné pamäťové zariadenia statického typu sa vyznačujú vysokou rýchlosťou a v mikroprocesorových systémoch sa používajú v obmedzenej miere kvôli ich relatívne vysokej cene. V takýchto systémoch sa používajú len ako takzvaná vyrovnávacia pamäť. Cache (rezerva) označuje vysokorýchlostnú vyrovnávaciu pamäť medzi procesorom a hlavnou pamäťou, ktorá slúži na čiastočnú kompenzáciu rozdielu v rýchlosti procesora a hlavnej pamäte – vkladajú sa do nej najčastejšie používané dáta. Pri prvom prístupe procesora k pamäťovej bunke sa jej obsah paralelne skopíruje do vyrovnávacej pamäte a v prípade opakovaného prístupu je možné ho z nej získať oveľa vyššou rýchlosťou. Pri zápise do pamäte sa informácie dostanú do vyrovnávacej pamäte a súčasne sa skopírujú do pamäte (schéma Write Through - priamy alebo prostredníctvom zápisu) alebo sa po chvíli skopírujú (schéma Write Back - spätný zápis). Pri spätnom zápise, nazývanom aj prechod do vyrovnávacej pamäte, sa informácie skopírujú do pamäte v prvom voľnom cykle a pri oneskorenom zápise (oneskorený zápis) - keď nie je voľná oblasť na umiestnenie novej hodnoty do vyrovnávacej pamäte; zároveň sú pomerne málo používané dáta vytlačené do hlavnej RAM. Druhá schéma je efektívnejšia, ale aj zložitejšia kvôli potrebe udržiavať konzistentný obsah vyrovnávacej pamäte a hlavnej pamäte.

Pamäť cache pozostáva z dátovej oblasti rozdelenej na bloky (riadky), ktoré sú elementárnymi jednotkami informácií počas prevádzky cache, a z oblasti tagov, ktorá popisuje stav riadkov (voľné, zaneprázdnené, označené na zápis atď.). V zásade sa používajú dve schémy organizácie vyrovnávacej pamäte: priama mapovaná, keď každá adresa pamäte môže byť uložená do vyrovnávacej pamäte iba jedným riadkom (v tomto prípade je číslo riadku určené nižšími bitmi adresy), a asociatívna ra-way, keď každý adresu možno uložiť do vyrovnávacej pamäte vo viacerých riadkoch. Asociatívna vyrovnávacia pamäť je zložitejšia, ale umožňuje väčšiu flexibilitu pri ukladaní údajov do vyrovnávacej pamäte; najbežnejšie sú štvorlinkové systémy vyrovnávacej pamäte.

Mikroprocesory 486 a vyššie majú tiež internú (Internú) vyrovnávaciu pamäť 8...16 KB. Označuje sa tiež ako Primárna (primárna) alebo LI (Úroveň I - prvá úroveň), na rozdiel od vonkajšej (Externá), umiestnená na doske a označená ako Sekundárna (sekundárna) alebo L2. Vo väčšine procesorov interná vyrovnávacia pamäť funguje podľa schémy priameho zápisu a v 486 (procesor Intel P24D a najnovší DX4-100, AMD DX4-120, 5x86) a Pentiu dokáže pracovať aj s lenivým zápisom. Ten vyžaduje špeciálnu podporu základnej dosky, takže pri výmene cez DMA (priamy prístup do pamäte k vstupným/výstupným zariadeniam) je možné zachovať konzistenciu dát v pamäti a vnútornej vyrovnávacej pamäti. Procesory Pentium Pro majú tiež vstavanú vyrovnávaciu pamäť L2 s veľkosťou 256 alebo 512 KB.

V mikroprocesorových systémoch sa ako RAM najčastejšie používa dynamická RAM s úložným kondenzátorom, ktoré sú veľmi rôznorodé. Uvádzame údaje o najbežnejších typoch takýchto RAM.

V dynamickej pamäti sa bunky vyrábajú na základe oblastí s akumuláciou náboja, ktoré zaberajú oveľa menšiu plochu ako spúšťače a prakticky nespotrebúvajú energiu pri ukladaní informácií. Keď sa do takejto bunky zapíše bit, vytvorí sa v nej elektrický náboj, ktorý pretrváva niekoľko milisekúnd; pre trvalú úsporu náboja článku je potrebné zregenerovať (prepísať) jeho obsah. Bunky dynamických pamäťových čipov sú tiež organizované v obdĺžnikovej matici; pri prístupe k mikroobvodu sa na jeho vstupy najskôr dodáva adresa riadka matice, sprevádzaná signálom RAS (Row Address Strobe - stroboskop riadkovej adresy), potom po chvíli adresa stĺpca sprevádzaná signálom CAS (Strobe adresy stĺpca - stroboskop adresy stĺpca). Pri každom prístupe k jednotlivej bunke sa regenerujú všetky bunky zvoleného riadku, takže na úplnú regeneráciu matice stačí vyčísliť adresy riadkov. Dynamické pamäťové bunky majú relatívne nízku rýchlosť (desiatky - stovky nanosekúnd), ale vysokú špecifickú hustotu (rádovo niekoľko megabajtov na balík) a nižšiu spotrebu energie.

Bežná RAM sa často nazýva asynchrónna, keďže nastavenie adresy a dodávanie riadiacich signálov je možné vykonávať v ľubovoľných časoch, je potrebné len dodržať časovanie medzi týmito signálmi. Zahŕňajú takzvané ochranné intervaly potrebné na vytvorenie signálov. Existujú aj synchrónne typy pamätí, ktoré prijímajú externý hodinový signál, na impulzy ktorých sú pevne viazané momenty odoslania adresy a výmeny údajov; umožňujú úplnejšie využitie vnútorného potrubia a blokujú prístup.

V poslednej dobe sa aktívne používa FPM DRAM (Fast Page Mode DRAM - dynamická pamäť s rýchlym prístupom na stránku). Stránkovaná pamäť sa líši od klasickej dynamickej pamäte tým, že po výbere riadku matice a podržaní signálu RAS umožňuje viacnásobné nastavenie adresy stĺpca hradlovanej signálom CAS, ako aj rýchlu regeneráciu podľa schémy „CAS pred RAS“ . Prvý vám umožňuje urýchliť prenosy blokov, keď je celý dátový blok alebo jeho časť v jednom riadku matice, ktorý sa v tomto systéme nazýva stránka, a druhý - skrátiť čas strávený regeneráciou pamäte.

EDO (Extended Data Out - predĺžený čas držania dát na výstupe) sú vlastne obyčajné FPM mikroobvody, na výstupe ktorých sú nainštalované dátové západky. So stránkovaním takéto mikroobvody pracujú v jednoduchom pipeline režime: na dátových výstupoch uchovávajú obsah poslednej vybranej bunky, zatiaľ čo adresa ďalšej vybranej bunky je už privádzaná na ich vstupy. To umožňuje zrýchliť proces čítania sekvenčných dátových polí približne o 15 % v porovnaní s FPM. Pri náhodnom adresovaní sa takáto pamäť nelíši od bežnej pamäte.

BEDO (Burst EDO - EDO s blokovým prístupom) je pamäť založená na EDO, ktorá nepracuje v jednotlivých, ale v dávkových cykloch čítania/zápisu. Moderné procesory si vďaka internému a externému cachovaniu inštrukcií a dát vymieňajú s hlavnou pamäťou hlavne bloky slov maximálnej šírky. S prítomnosťou pamäte BEDO nie je potrebné neustále dodávať sériové adresy na vstupy mikroobvodov s potrebnými časovými oneskoreniami, stačí prechod na ďalšie slovo hradiť samostatným signálom.

SDRAM (Synchronous DRAM – synchrónna dynamická pamäť) – pamäť so synchrónnym prístupom, beží rýchlejšie ako konvenčné asynchrónne (FPM / EDO / BEDO). Okrem synchrónneho prístupu SDRAM využíva vnútorné rozdelenie pamäťového poľa na dve nezávislé banky, čo umožňuje kombinovať načítanie z jednej banky s nastavením adresy v inej. SDRAM podporuje aj výmenu blokov. Hlavnou výhodou SDRAM je, že podporuje sekvenčný prístup v synchrónnom režime, kde nie sú potrebné žiadne ďalšie cykly spánku. S náhodným prístupom pracuje SDRAM takmer rovnakou rýchlosťou ako FPM/EDO.

Pipeline Burst SRAM (Pipelined Burst SRAM) je typ synchrónnej SRAM s interným pipeliningom, ktorý zhruba zdvojnásobuje rýchlosť výmeny dátových blokov.

Okrem hlavnej pamäte RAM je zariadenie na zobrazovanie informácií vybavené aj pamäťovým zariadením - systémom zobrazovania videa. Táto pamäť sa nazýva video pamäť a nachádza sa na doske grafického adaptéra.

Videopamäť sa používa na ukladanie obrazu. Maximálne možné rozlíšenie grafickej karty závisí od jej objemu - AxBxC, kde A je počet bodov vodorovne, B zvisle, C počet možných farieb pre každý bod. Napríklad pre rozlíšenie 640x480x16 stačí mať video pamäť 256 KB, pre 800x600x256 - 512 KB, pre 1024x768x65536 (iné označenie je 1024x768x64k) - 2 MB, atď. Keďže farby sú uložené v celočíselnom počte bitov, počet farieb je vždy celočíselná mocnina 2 (16 farieb - 4 bity, 256 - 8 bitov, 64k - 16 atď.).

Video adaptéry používajú nasledujúce typy videopamäte.

FPM DRAM (Fast Page Mode Dynamic RAM - dynamická RAM s rýchlym prístupom k stránke) je hlavným typom video pamäte, identickej s tou, ktorá sa používa na základných doskách. Aktívne sa používal až do roku 1996. Najbežnejšie čipy FPM DRAM sú štvorbitové DIP a SOJ, ako aj šestnásťbitové SOJ.

VRAM (Video RAM - video RAM) - takzvaná dvojportová DRAM s podporou súčasného prístupu z video procesora a centrálneho procesora počítača. Umožňuje časovo kombinovať zobrazenie obrazu na obrazovke a jeho spracovanie vo videopamäti, čo znižuje oneskorenia a zvyšuje rýchlosť práce.

EDO DRAM (Extended Data Out DRAM - dynamická RAM s predĺženým časom uchovávania dát na výstupe) - pamäť s pipeliningovými prvkami, ktorá umožňuje mierne urýchliť výmenu dátových blokov s video pamäťou.

SGRAM (Synchronous Graphics RAM - synchronous graphics RAM) - variant DRAM so synchrónnym prístupom, kedy sa všetky riadiace signály menia súčasne so signálom systémových hodín, čo znižuje časové oneskorenia.

WRAM (Window RAM - windowed RAM) - EDO VRAM, v ktorej je okno, cez ktoré pristupuje ovládač videa, menšie ako okno pre CPU.

MDRAM (Multibank DRAM - multi-bank RAM) je variant DRAM organizovaný vo forme mnohých nezávislých bánk s veľkosťou 32 KB, ktoré pracujú v zreťazovanom režime.

Zvýšenie rýchlosti videoprocesora pristupujúceho k videopamäti okrem zvýšenia priepustnosti adaptéra umožňuje zvýšiť maximálnu frekvenciu regenerácie obrazu, čo znižuje únavu očí operátora.

Pamäťové čipy majú štyri hlavné charakteristiky – typ, veľkosť, štruktúru a čas prístupu. Typ označuje statickú alebo dynamickú pamäť, objem udáva celkovú kapacitu pamäte a štruktúra udáva počet pamäťových buniek a bitovú šírku každej bunky. Napríklad 28/32-pin SRAM DIP čipy majú 8-bitovú štruktúru (8kx8, 16kx8, 32kx8, 64kx8, 128kx8), 256 KB cache pozostáva z ôsmich 32kx8 čipov alebo štyroch 64kx8 čipov (hovoríme o dátovej oblasti , dodatočné čipy na ukladanie prvkov môžu mať inú štruktúru). Dva mikroobvody 128kx8 už nie je možné dodať, pretože je potrebná 32-bitová dátová zbernica, ktorú môžu zabezpečiť iba štyri mikroobvody. Bežné SRAM RT v 100-pinových PQFP puzdrách majú 32-bitovú štruktúru 32kx32 alebo 64kx32 a používajú sa dva alebo štyri v doskách Pentium.

30-kolíkové moduly SIMM majú 8-bitovú štruktúru a používajú sa s procesormi 286, 386SX a 486SLC po dvoch a po štyroch s 386DX, 486DLC a bežným 486DX. 72-kolíkové moduly SIMM majú 32-bitovú štruktúru a možno ich použiť jeden po druhom s 486DX a dva naraz s Pentium a Pentium Pro. 168-kolíkové moduly DIMM majú 64-bitovú štruktúru a používajú sa v zariadeniach Pentium a Pentium Pro jeden po druhom. Inštalácia väčšieho ako minimálneho počtu pamäťových modulov alebo cache čipov pre danú systémovú (základnú dosku) dosku umožňuje urýchliť prácu s nimi pomocou princípu interleave.

Čas prístupu charakterizuje rýchlosť mikroobvodu a zvyčajne sa uvádza v nanosekundách za pomlčkou na konci názvu. Na pomalších mikroobvodoch je možné uviesť iba prvé číslice (-7 namiesto -70, -15 namiesto -150), na rýchlejších statických "-15" alebo "-20" označuje skutočný čas prístupu k bunke . Mikroobvody často označujú minimum všetkých možných prístupových časov, napríklad označenie 50 EDO DRAM namiesto 70 alebo 45 namiesto 60 je bežné, hoci takýto cyklus je možné dosiahnuť iba v blokovom režime a v jedinom režime je čip stále má prístupovú dobu 70 alebo 60 ns. Podobná situácia nastáva pri označení SRAM PB: 6 namiesto 12 a 7 namiesto 15. Čipy SDRAM sú zvyčajne označené dobou prístupu v blokovom režime (10 alebo 12 ns).

Pamäťové integrované obvody sú implementované v nasledujúcich typoch balíkov.

DIP (Dual In line Package - balík s dvoma radmi kolíkov) - klasické mikroobvody používané v hlavných pamäťových blokoch IBM PC / XT a skorých PC / AT sa teraz používajú v blokoch vyrovnávacej pamäte.

SIP (Single In line Package - balenie s jedným radom kolíkov) - mikroobvod s jedným radom kolíkov, inštalovaný vertikálne.

SIPP (Single In line Pinned Package - modul s jedným radom kolíkov) - pamäťový modul vložený do panelu ako čipy DIP / SIP; používané v skorých IBM PC/AT.

SIMM (Single In line Memory Module – pamäťový modul s jedným radom kontaktov) – pamäťový modul vložený do svorkového konektora; používa sa vo všetkých moderných doskách, ako aj v mnohých adaptéroch, tlačiarňach a iných zariadeniach. SIMM má kontakty na oboch stranách modulu, ale všetky sú prepojené a tvoria akoby jeden rad kontaktov. SIMM sú v súčasnosti vybavené hlavne čipmi FPM/EDO/BEDO.

DIMM (Dual Inline Memory Module - pamäťový modul s dvoma radmi kontaktov) je pamäťový modul podobný SIMM, ale so samostatnými kontaktmi (zvyčajne 2x84), čím sa zvyšuje bitová hĺbka alebo počet pamäťových bánk v module. Používa sa najmä v počítačoch Apple a nových doskách P5 a P6. Moduly DIMM sú vybavené čipmi EDO/BEDO/SDRAM.

CELP (Card Egde Low Profile - nízka karta s nožovým konektorom) je modul externej vyrovnávacej pamäte zostavený na čipoch SRAM (asynchrónne) alebo RV SRAM (synchrónne). Vyzerá podobne ako 72-kolíkový SIMM, má kapacitu 256 alebo 512 KB. Iný názov je COAST (Cache On A STick – doslova „keška na palici“).

Dynamické pamäťové moduly môžu mať okrem hlavných pamäťových buniek ďalšie bunky na ukladanie paritných bitov (Parita) pre dátové bajty; takéto SIMM sa niekedy označujú ako 9- a 36-bitové moduly (jeden paritný bit na dátový bajt). Paritné bity sa používajú na kontrolu správnosti čítania údajov z modulu, čo vám umožňuje odhaliť niektoré chyby (pozri časť 9.7). Moduly s paritnými bitmi má zmysel používať len tam, kde je potrebná veľmi vysoká spoľahlivosť. Pre bežné aplikácie sú vhodné aj starostlivo testované moduly bez paritných bitov, avšak za predpokladu, že základná doska tieto typy modulov podporuje.

Najjednoduchší spôsob, ako určiť typ modulu, je označenie a počet pamäťových čipov na ňom: ak má napríklad 30-kolíkový SIMM dva čipy rovnakého typu a jeden ďalší, potom prvé dva sú hlavné (každý so štyrmi číslicami) a tretí je určený na uloženie paritných bitov (je jednobitový).

V 12-čipovej 72-kolíkovej SIMM, osem z nich ukladá dáta a štyri paritné bity. Moduly s 2, 4 alebo 8 čipmi nemajú paritnú pamäť.

Niekedy je na moduloch umiestnený takzvaný simulátor parity - sčítací čip, ktorý pri čítaní bunky vždy vytvára správny paritný bit. Toto je určené hlavne na inštaláciu takýchto modulov do dosiek, kde nie je vypnutá kontrola parity.

72-pinové moduly SIMM majú štyri špeciálne linky PD (Presence Detect), na ktorých je možné pomocou prepojok nastaviť až 16 kombinácií signálov. Linky PD sa používajú v niektorých základných doskách na určenie prítomnosti pamäťových modulov v slotoch a ich parametrov (kapacita a rýchlosť). Väčšina univerzálnych dosiek tretích strán, podobne ako ich SIMM, nepoužívajú linky PD.

V moduloch DIMM v súlade so špecifikáciou JEDEC je technológia PD implementovaná pomocou prepisovateľnej ROM so sériovým prístupom (Serial EEPROM) a nazýva sa Serial Presence Detect (SPD). ROM je 8-pinový mikročip umiestnený v rohu dosky DIMM a jeho obsah popisuje konfiguráciu a parametre modulu. Základné dosky s čipovou sadou 440LX/BX môžu použiť SPD na konfiguráciu systému správy pamäte. Niektoré základné dosky dokážu obísť SPD konfiguráciou modulov obvyklým spôsobom.

Kontrolné otázky a úlohy

1. Aké typy pamäte existujú?

2. Simulujte statickú pamäťovú bunku na obr. 9.46. Úlohou simulácie je vybrať binárne kombinácie pre signály na vstupe bunky a zaznamenať výsledok na výstupe bunky pomocou indikátora IND.

3. Na základe diagramu na obr. 9.45 navrhnite štvorbitový obvod RAM pomocou generátora slov. Zároveň je v schéme na obr. 9.45 používať iba 4 nižšie adresy (dve v riadkoch a dve v stĺpcoch) a teda iba dve dátové zbernice (dve vstupné a dve výstupné). Pripojte indikátory na výstupné zbernice.

4. Kde sa v moderných počítačoch používa pamäť statického typu?

5. Aký je rozdiel medzi dynamickou pamäťou a statickou pamäťou?

6. Aké typy dynamickej pamäte sa používajú v moderných počítačoch?

7. Čo je to video pamäť a ako súvisí s charakteristikami informácií zobrazených na displeji?

8. Aké typy pamäte sa používajú ako video pamäť?

9. Aký je dizajn pamäťových čipov?

V počítači je oveľa dynamickejšia pamäť ako statická pamäť, pretože je to DRAM, ktorá sa používa ako hlavná pamäť VM. Podobne ako SRAM, aj dynamická pamäť pozostáva z jadra (ZE pole) a logiky rozhrania (bufferové registre, zosilňovače na čítanie dát, regeneračné obvody atď.). Hoci počet typov DRAM už presiahol dve desiatky, ich jadro je organizované takmer rovnako. Hlavné rozdiely súvisia s logikou rozhrania a tieto rozdiely sú spôsobené aj rozsahom mikroobvodov - okrem hlavnej pamäte VM sú integrované obvody dynamickej pamäte zahrnuté napríklad vo video adaptéroch. Klasifikácia dynamických pamäťových čipov je znázornená na obr. 5.10.

Aby sme pochopili rozdiely medzi typmi DRAM, pozrime sa najprv na algoritmus pre prácu s dynamickou pamäťou. Na to použijeme Obr. 5.6.

Na rozdiel od SRAM sa adresa bunky DRAM prenáša do mikroobvodu v dvoch krokoch, najprv adresa stĺpca a potom riadok, čo umožňuje znížiť počet kolíkov adresovej zbernice približne o polovicu, zmenšiť veľkosť balenia a umiestniť viac mikroobvodov na základnej dosky. To samozrejme vedie k poklesu výkonu, keďže prenos adresy trvá dvakrát dlhšie. Na označenie, ktorá časť adresy je v určitom okamihu prenášaná, sa používajú dva pomocné signály RAS a CAS. Pri prístupe k pamäťovej bunke sa adresa reťazca nastaví na adresovú zbernicu. Po stabilizácii procesov na zbernici je vydaný signál RAS a adresa je zapísaná do vnútorného registra mikroobvodu

Ryža. 5.10. Klasifikácia dynamickej RAM: a - čipy pre hlavnú pamäť; b - čipy pre video adaptéry

Pamäť. Adresa stĺpca sa potom nastaví na adresovej zbernici a vydá sa signál CAS. V závislosti od stavu linky WE sa dáta čítajú z bunky alebo zapisujú do bunky (pred zápisom je potrebné dáta umiestniť na dátovú zbernicu). Interval medzi nastavením adresy a vydaním signálu RAS (alebo CAS) je určený technickými charakteristikami mikroobvodu, ale zvyčajne sa adresa nastavuje v jednom cykle systémovej zbernice a riadiaci signál v ďalšom. Na čítanie alebo zápis jednej bunky DRAM je teda potrebných päť cyklov, v ktorých nastane nasledovné: vydanie adresy riadka, vydanie signálu RAS, vydanie adresy stĺpca, vydanie signálu CAS, vykonanie operácie čítania/zápisu (v statickej pamäti postup trvá len dva až tri ťahy).

Mali by ste si tiež uvedomiť potrebu regenerácie údajov. Ale spolu s prirodzeným vybitím kondenzátora GE v priebehu času vedie čítanie údajov z DRAM aj k strate náboja, takže po každej operácii čítania je potrebné údaje obnoviť. To sa dosiahne prepísaním rovnakých údajov ihneď po prečítaní. Pri čítaní informácií z jednej bunky sa v skutočnosti naraz rozdajú údaje z celého vybraného riadku, ale použijú sa iba tie, ktoré sú v stĺpci záujmu, a všetky ostatné sa ignorujú. Operácia čítania z jednej bunky teda vedie k zničeniu údajov celého riadku a je potrebné ich obnoviť. Regenerácia dát po načítaní prebieha automaticky logikou rozhrania čipu a deje sa tak ihneď po načítaní riadku.

Teraz sa pozrime na rôzne typy dynamických pamäťových čipov, počnúc systémovými DRAM, teda čipmi určenými na použitie ako hlavná pamäť. V počiatočnom štádiu to boli asynchrónne pamäťové mikroobvody, ktorých činnosť nebola pevne viazaná na hodinové impulzy systémovej zbernice.

Asynchrónna dynamická RAM. Asynchrónne dynamické čipy RAM sú riadené signálmi RAS a CAS a ich činnosť v zásade priamo nesúvisí s hodinami zbernice. Asynchrónna pamäť je charakterizovaná dodatočným časom stráveným interakciou pamäťových čipov a radiča. Takže v asynchrónnom obvode bude signál RAS generovaný až po príchode hodinového impulzu do ovládača a bude vnímaný pamäťovým čipom po určitom čase. čas. Potom pamäť vydá údaje, ale ovládač ich bude môcť prečítať až po príchode ďalšieho hodinového impulzu, od ktorého by mal pracovať synchrónne so zvyškom zariadení VM. Počas cyklu čítania/zápisu teda dochádza k malým oneskoreniam v dôsledku čakania pamäte radiča a pamäťového radiča.

MikroobvodyDRAM. Prvé dynamické pamäťové čipy využívali najjednoduchší spôsob výmeny dát, často nazývaný tradičný. Umožňoval čítať a zapisovať riadok pamäte iba v každom piatom cykle (obr. 5.11, a). Kroky tohto postupu boli opísané vyššie. Tradičná DRAM zodpovedá vzorcu 5-5-5-5. Čipy tohto typu mohli pracovať na frekvenciách do 40 MHz a pre svoju pomalosť (prístupová doba bola cca 120 ns) dlho nevydržali.

MikroobvodyFPM DRAM. Čipy DRAM, ktoré implementujú režim FPM, sú tiež prvými typmi DRAM. Podstata režimu sa ukázala skôr. Schéma čítania pre FPM DRAM (obr. 5.11, b) je opísaná vzorcom 5-3-3-3 (celkovo 14 cyklov). Použitie schémy rýchleho stránkovania znížilo prístupový čas na 60 ns, čo pri zohľadnení schopnosti pracovať na vyšších frekvenciách zbernice viedlo k zvýšeniu výkonu pamäte o cca 70 % v porovnaní s tradičnou DRAM. Tento typ mikročipu sa používal v osobných počítačoch približne do roku 1994.

MikroobvodyEDO DRAM. Ďalším krokom vo vývoji dynamickej pamäte RAM boli integrované obvody s režim hyperstránky, prístup(HPM, Hyper Page Mode), známejšie ako EDO (Extended Data Output – predĺžený čas uchovávania dát na výstupe). Hlavnou črtou technológie je dlhší čas dostupnosti dát na výstupe čipu v porovnaní s FPM DRAM. V čipoch FPM DRAM zostávajú výstupné dáta platné iba vtedy, keď je aktívny signál CAS, a preto druhý a ďalší prístup k linke vyžaduje tri cykly: cyklus prepínania CAS do aktívneho stavu, cyklus čítania dát a CAS prepnúť cyklus do neaktívneho stavu. V EDO DRAM sa na aktívnej (zostupnej) hrane signálu CAS dáta uložia do interného registra, kde sa uložia ešte nejaký čas po príchode ďalšej aktívnej hrany signálu. To umožňuje použiť uložené údaje, keď je CAS už neaktívny (obrázok 5.11, v)

Inými slovami, časové parametre sa zlepšujú vďaka eliminácii čakacích cyklov na moment stabilizácie dát na výstupe mikroobvodu.

Čítacia schéma EDO DRAM je už 5-2-2-2, čo je o 20 % rýchlejšie ako FPM. Čas prístupu je asi 30-40 ns. Je potrebné poznamenať, že maximálna frekvencia systémovej zbernice pre čipy EDO DRAM by nemala presiahnuť 66 MHz.

MikroobvodyBEDO DRAM. Technológia EDO bola vylepšená spoločnosťou VIA Technologies. Nová modifikácia EDO je známa ako BEDO (Burst EDO - dávkové EDO). Novinkou metódy je, že pri prvom prístupe sa načíta celý riadok mikroobvodu, ktorý obsahuje po sebe idúce slová paketu. Sekvenčný prenos slov (prepínanie stĺpcov) je automaticky monitorovaný vnútorným počítadlom mikroobvodu. To eliminuje potrebu vydávať adresy pre všetky bunky v pakete, ale vyžaduje si podporu externej logiky. Metóda umožňuje skrátiť čas čítania druhého a nasledujúcich slov o jeden cyklus (obr. 5.11, d), vďaka čomu má vzorec tvar 5-1-1-1.

5.11. Časové diagramy rôznych typov asynchrónnej dynamickej pamäte s dĺžkou paketu štyroch slov: a - tradičná DRAM; b - FPM FRAM; v- EDO DRAM;

G - BEDO DRAM

MikroobvodyEDRAM. Rýchlejšiu verziu DRAM vyvinula Enhanced Memory Systems, divízia Ramtronu. Technológia je implementovaná vo variantoch FPM, EDO a BEDO. Čip má rýchlejšie jadro a vnútornú vyrovnávaciu pamäť. Prítomnosť druhého je hlavnou črtou technológie. Cache pamäť je statická pamäť (SRAM) s kapacitou 2048 bitov. Jadro EDRAM má 2048 stĺpcov, z ktorých každý je pripojený k vnútornej vyrovnávacej pamäti. Pri prístupe k ľubovoľnej bunke sa súčasne načíta celý riadok (2048 bitov). Čítací riadok sa vkladá do SRAM a prenos informácií do vyrovnávacej pamäte nemá prakticky žiadny vplyv na výkon, pretože prebieha v jednom hodinovom cykle. Pri ďalších prístupoch k bunkám patriacim do rovnakého riadku sa údaje preberajú z rýchlejšej vyrovnávacej pamäte. K ďalšiemu volaniu jadra dôjde pri prístupe k bunke, ktorá sa nenachádza v riadku čipu uloženého vo vyrovnávacej pamäti.

Táto technológia je najúčinnejšia pre sekvenčné čítanie, to znamená, keď sa priemerný čas prístupu pre mikroobvod blíži k hodnotám typickým pre statickú pamäť (asi 10 ns). Hlavný problém spočíva v nekompatibilite s ovládačmi používanými pri práci s inými typmi DRAM

Synchrónna dynamická RAM. V synchrónnych DRAM je výmena informácií synchronizovaná externými hodinovými signálmi a prebieha v presne definovaných časových bodoch, čo umožňuje plne využiť šírku pásma zbernice procesor-pamäť a vyhnúť sa čakacím cyklom. Adresa a riadiace informácie sú zaznamenané v pamäťovom IC. Potom nastane odozva mikroobvodu po dobre definovanom počte hodinových impulzov a procesor môže tento čas využiť na iné akcie, ktoré nesúvisia s prístupom do pamäte. Pri synchrónnej dynamickej pamäti namiesto trvania prístupového cyklu hovoria o minimálnej prípustnej perióde taktovacej frekvencie a to už hovoríme o čase rádovo 8-10 ns.

MikroobvodySDRAM. Skratka SDRAM (Synchronous DRAM – synchrónna DRAM) sa používa na označenie čipov „normálnej“ synchrónnej dynamickej RAM. Základné rozdiely medzi SDRAM a asynchrónnou dynamickou RAM diskutovanou vyššie možno zredukovať na štyri body:

Synchrónny spôsob prenosu dát na zbernicu;

Dopravný mechanizmus na prepravu balíka;

Použitie niekoľkých (dvoch alebo štyroch) vnútorných pamäťových bánk;

Prenos časti funkcií pamäťového radiča na logiku samotného mikroobvodu.

Synchronizácia pamäte umožňuje pamäťovému radiču „vedieť“, kedy sú dáta pripravené, čím sa znižuje réžia čakania a hľadania dát. Keďže dáta sa objavujú na výstupe IC súčasne s hodinovými impulzmi, interakcia pamäte s inými VM zariadeniami je zjednodušená.

Na rozdiel od BEDO, pipeline umožňuje prenos paketových dát pomocou hodinových cyklov – vďaka čomu môže RAM plynulo pracovať na vyšších frekvenciách ako asynchrónna RAM. Výhody pipeline sa zvyšujú najmä pri prenose dlhých paketov, ktoré však nepresahujú dĺžku čipovej linky.

Významný účinok sa dosiahne rozdelením celej sady buniek do nezávislých vnútorných polí (banky). To umožňuje spojiť prístup do bunky jednej banky s prípravou na ďalšiu operáciu v iných bankách (dobíjanie riadiacich obvodov a obnova informácií). Schopnosť ponechať otvorených niekoľko riadkov pamäte súčasne (z rôznych bánk) tiež zlepšuje výkon pamäte. Pri sekvenčnom prístupe k bankám frekvencia prístupu ku každej z nich individuálne klesá úmerne počtu bánk a SDRAM môže pracovať na vyšších frekvenciách. Vďaka vstavanému čítaču adries umožňuje SDRAM, podobne ako BEDO DRAM, čítanie a zápis v burst režime a v SDRAM sa mení dĺžka paketu a v burst režime je možné prečítať celý pamäťový riadok. IC možno charakterizovať vzorcom 5-1-1-1. Aj keď vzorec pre tento typ dynamickej pamäte je rovnaký ako u BEDO, schopnosť pracovať na vyšších frekvenciách znamená, že SDRAM s dvoma 6ankmi na hodinovej frekvencii 100 MHz zbernice dokáže takmer zdvojnásobiť výkon pamäte typu BEDO.

MikroobvodyDDR SDRAM. Dôležitým krokom v ďalšom vývoji technológie SDRAM bola DDR SDRAM (Double Data Rate SDRAM – SDRAM s dvojnásobnou rýchlosťou prenosu dát). Na rozdiel od SDRAM nová modifikácia dodáva dáta v burst móde na oboch hranách synchronizačného impulzu, vďaka čomu je priepustnosť dvojnásobná. Existuje niekoľko špecifikácií DDR SDRAM v závislosti od taktovacej frekvencie systémovej zbernice: DDR266, DDR333, DDR400, DDR533. Špičková šírka pásma pamäťového čipu DDR333 je teda 2,7 GB / s a pre DDR400 - 3,2 GB / s. DDR SDRAM je v súčasnosti najbežnejším typom dynamickej pamäte v osobných VM.

MikroobvodyRDRAM, DRDRAM. Najzrejmejším spôsobom, ako zvýšiť efektivitu procesora s pamäťou, je zvýšiť frekvenciu hodín zbernice alebo šírku vzorky (počet bitov odoslaných súčasne). Bohužiaľ, pokusy o kombináciu oboch možností narážajú na značné technické ťažkosti (so zvýšením frekvencie sa problémy s elektromagnetickou kompatibilitou zhoršujú, je ťažšie zabezpečiť súčasný príjem všetkých bitov informácií prenášaných paralelne k spotrebiteľovi). Väčšina synchrónnych DRAM (SDRAM, DDR) používa široké vzorkovanie (64 bitov) s obmedzenou frekvenciou zbernice.

Zásadne odlišný prístup k budovaniu DRAM navrhol Rambus v roku 1997. Zameriava sa na zvýšenie taktovacej frekvencie na 400 MHz pri súčasnom znížení šírky vzorky na 16 bitov. Nová pamäť je známa ako RDRAM (Rambus Direct RAM). Existuje niekoľko druhov tejto technológie: Base, Concurrent a Direct. Celkovo sa taktovanie vykonáva na oboch okrajoch hodinových signálov (ako v DDR), vďaka čomu je výsledná frekvencia 500-600, 600-700 a 800 MHz. Prvé dve možnosti sú takmer totožné, no zmeny v technológii Direct Rambus sú dosť výrazné.

Najprv sa zastavme pri základných aspektoch technológie RDRAM, pričom sa zameriame hlavne na modernejšiu verziu – DRDRAM. Hlavným rozdielom od ostatných typov DRAM je originálny systém výmeny dát medzi jadrom a pamäťovým radičom, ktorý je založený na takzvanom „Rambus channel“, ktorý využíva asynchrónny blokovo orientovaný protokol. Na logickej úrovni sa informácie medzi radičom a pamäťou prenášajú v paketoch.

Existujú tri typy paketov: dátové pakety, riadkové pakety a stĺpcové pakety. Pakety riadkov a stĺpcov slúžia na prenos príkazov z pamäťového radiča na ovládanie riadkov riadkov a stĺpcov poľa pamäťových prvkov, resp. Tieto inštrukcie nahrádzajú konvenčný čipový riadiaci systém signálmi RAS, CAS, WE a CS.

Pole GE je rozdelené do bánk. Ich počet v kryštáli s kapacitou 64 Mbit je 8 nezávislých alebo 16 duálnych bánk. V duálnych bankách má pár bánk spoločné zosilňovače na čítanie/zápis. Vnútorné jadro mikroobvodu má 128-bitovú dátovú zbernicu, ktorá umožňuje preniesť 16 bajtov na každú adresu stĺpca. Pri zápise môžete použiť masku, v ktorej každý bit zodpovedá jednému bajtu paketu. Pomocou masky môžete určiť, koľko bajtov paketu a ktoré sa majú zapísať do pamäte.

Dátové, riadkové a stĺpcové riadky v kanáli sú úplne nezávislé, takže riadkové príkazy, stĺpcové príkazy a dáta možno prenášať súčasne a pre rôzne čipové banky. Stĺpcové pakety obsahujú dve polia a sú prenášané cez päť riadkov. Prvé pole určuje hlavnú operáciu zápisu alebo čítania. Druhé pole obsahuje buď označenie použitia masky záznamu (samotná maska sa prenáša po dátových linkách), alebo rozšírený operačný kód, ktorý určuje variant pre hlavnú operáciu. Pakety riadkov sú rozdelené na príkazy aktivácie, zrušenia, obnovenia a vypínača. Na prenos linkových paketov sú pridelené tri linky.

Operácia zápisu môže bezprostredne nasledovať po čítaní - je potrebné iba oneskorenie počas prechodu signálu kanálom (od 2,5 do 30, bez ohľadu na dĺžku kanála). Pre vyrovnanie oneskorení pri prenose jednotlivých bitov prenášaného kódu musia byť vodiče na doske striktne rovnobežné, musia mať rovnakú dĺžku (dĺžka čiar by nemala presiahnuť 12 cm) a spĺňať prísne požiadavky určené vývojárom. .

Každý zápis v kanáli môže byť zreťazený, pričom oneskorenie prvého dátového paketu je 50 ns a zvyšok operácií čítania/zápisu sa vykonáva nepretržite (oneskorenie sa zavedie iba vtedy, keď sa operácia zmení zo zápisu na čítanie a naopak naopak).

Dostupné publikácie uvádzajú prácu spoločností Intel a Rambus na novej verzii RDRAM s názvom nDRAM, ktorá bude podporovať prenosové rýchlosti až do 1600 MHz.

MikroobvodySLDRAM. Potenciálnym konkurentom RDRAM pre úlohu štandardu architektúry pamäte pre budúce osobné VM je nový typ dynamickej RAM vyvinutý konzorciom výrobcov VM SyncLm Consortium a známy pod skratkou SLDRAM. Na rozdiel od RDRAM, ktorej technológia je majetkom spoločností Rambus a Intel, je tento štandard otvorený. Na systémovej úrovni sú technológie veľmi podobné. Dáta a príkazy z riadiacej jednotky do pamäte a späť do SLDRAM sa prenášajú v paketoch s n alebo 8 balíkmi. Príkazy, adresy a riadiace signály sa odosielajú cez jednosmernú 10-bitovú príkazovú zbernicu. Čítanie a zápis dát sa dodáva cez obojsmernú 18-bitovú dátovú zbernicu. Oba autobusy premávajú na rovnakej frekvencii. Táto frekvencia je zatiaľ stále 200 MHz, čo je vďaka technológii DDR ekvivalent 400 MHz. Ďalšie generácie SLDRAM by mali pracovať na frekvencii 400 MHz a vyššej, teda poskytovať efektívnu frekvenciu vyššiu ako 800 MHz.

K jednému ovládaču je možné pripojiť až 8 pamäťových čipov. Aby sa predišlo oneskoreniu signálu z mikroobvodov, ktoré sú od ovládača vzdialenejšie, určujú sa charakteristiky časovania pre každý mikroobvod a zadávajú sa do jeho riadiaceho registra pri zapnutí napájania.

MikroobvodyESDRAM. Toto je synchrónna verzia EDRAM, ktorá využíva rovnaké techniky redukcie prístupového času. Operácia zápisu, na rozdiel od operácie zápisu, obchádza vyrovnávaciu pamäť, čo zvyšuje výkon FSDRAM pri obnovení čítania z riadku, ktorý sa už nachádza vo vyrovnávacej pamäti. Vďaka prítomnosti dvoch bánk v čipe sú minimalizované prestoje kvôli príprave na operácie čítania/zápisu. Nevýhody uvažovaného mikroobvodu sú rovnaké ako nevýhody EDRAM - komplikácia regulátora, pretože musí brať do úvahy možnosť prípravy nového riadku jadra na čítanie do vyrovnávacej pamäte. Navyše, pri ľubovoľnom poradí adries sa vyrovnávacia pamäť využíva neefektívne.

MikroobvodyCDRAM. Tento typ pamäte RAM bol vyvinutý spoločnosťou Mitsubishi Corporation a možno ju považovať za revidovanú verziu ESDRAM bez niektorých jej nedokonalostí. Zmenila sa kapacita vyrovnávacej pamäte a princíp umiestňovania údajov do nej. Kapacita jedného bloku vyrovnávacej pamäte bola znížená na 128 bitov, takže 16-kilobitová vyrovnávacia pamäť môže súčasne ukladať kópie 128 pamäťových miest, čo umožňuje efektívnejšie využitie vyrovnávacej pamäte. Výmena prvej oblasti pamäte cache sa začne až po zaplnení posledného (128.) bloku. Zmenili sa aj spôsoby prístupu. Mikroobvod teda používa samostatné adresové zbernice pre statickú vyrovnávaciu pamäť a dynamické jadro. Prenos dát z dynamického jadra do vyrovnávacej pamäte je kombinovaný s vydávaním dát na zbernicu, takže časté, ale krátke prenosy neznižujú výkon IC pri čítaní veľkého množstva informácií z pamäte a vyrovnávajú CDRAM s ESDRAM , a pri čítaní na selektívnych adresách jednoznačne víťazí CDRAM. Treba však poznamenať, že vyššie uvedené zmeny viedli k ešte väčšej komplikácii pamäťového radiča.

Dynamická RAM(Dynamic RAM - DRAM) sa používa vo väčšine systémov RAM moderných počítačov. Hlavnou výhodou tohto typu pamäte je, že jej bunky sú veľmi husto zbalené, t.j. veľa bitov sa dá zbaliť do malého čipu, čo znamená, že na ich základe možno organizovať veľkokapacitnú pamäť.

Pamäťové bunky v čipe DRAM sú malé kondenzátory, ktoré uchovávajú náboje. Takto (prítomnosť alebo neprítomnosť nábojov) sú bity kódované. Problémy spojené s týmto typom pamäte sú spôsobené tým, že je dynamická, t.j. sa musí neustále regenerovať, inak sa elektrické náboje v pamäťových kondenzátoroch „vyčerpajú“ a dáta sa stratia. Obnovenie nastane, keď si pamäťový radič systému urobí malú prestávku a pristúpi ku všetkým dátovým linkám v pamäťových čipoch. Väčšina systémov má pamäťový radič (zvyčajne zabudovaný do čipsetu základnej dosky, ale môže byť zabudovaný aj do procesora, ako v procesoroch Athlon 64 a Opteron), ktorý je nastavený na priemyselnú štandardnú obnovovaciu frekvenciu 15 ms. To znamená, že každých 15 ms sa načítajú všetky riadky v pamäti, aby sa zabezpečilo obnovenie údajov.

Regenerácia pamäte, žiaľ, zaberá čas od procesora. Každý regeneračný cyklus trvá niekoľko cyklov CPU. V starších počítačoch môžu obnovovacie cykly trvať až 10 % (alebo viac) času procesora, ale v moderných systémoch sú tieto náklady nižšie ako 1 %. Niektoré systémy umožňujú zmeniť nastavenia regenerácie pomocou programu nastavenia systému BIOS. Interval medzi aktualizačnými cyklami sa nazýva tREF a nenastavuje sa v milisekundách, ale v hodinových cykloch. Je veľmi dôležité pochopiť, že zvýšenie hodnoty intervalu obnovy na zlepšenie výkonu systému môže viesť k náhodným náhodným chybám.

Náhodná chyba je chyba spracovania údajov, ktorá nesúvisí s poruchou pamäťového čipu. Vo väčšine prípadov je bezpečnejšie držať sa odporúčanej alebo predvolenej obnovovacej frekvencie. Keďže náklady na obnovenie v moderných počítačoch sú nižšie ako 1 %, zmena obnovovacej frekvencie má malý vplyv na výkon počítača. Jednou z najprijateľnejších možností je použiť na synchronizáciu pamäte predvolené hodnoty alebo automatické nastavenia špecifikované pomocou programu Setup BIOS. Väčšina moderných systémov vám neumožňuje zmeniť zadané časovanie pamäte, vždy pomocou automaticky nastavených parametrov.

Zariadenia DRAM využívajú na uloženie jedného bitu len jeden tranzistor a dvojicu kondenzátorov, takže sú priestrannejšie ako iné typy pamäťových čipov. V súčasnosti sa už vyrábajú dynamické čipy RAM s kapacitou 4 GB a viac. To znamená, že takéto mikroobvody obsahujú viac ako miliardu tranzistorov! Ale procesor Core 2 Duo má len 230 miliónov tranzistorov. Prečo taký rozdiel? Faktom je, že v pamäťovom čipe sú všetky tranzistory a kondenzátory umiestnené v sérii, zvyčajne v uzloch štvorcovej mriežky, vo forme veľmi jednoduchých, periodicky sa opakujúcich štruktúr, na rozdiel od procesora, ktorý je zložitejším obvodom. rôznych štruktúr, ktoré nemajú jasnú organizáciu.

Tranzistor každého jednobitového registra DRAM sa používa na čítanie stavu susedného kondenzátora. Ak je kondenzátor nabitý, článok ho obsahuje; ak nie je poplatok, napíše sa nula. Náboje v maličkých kondenzátoroch sa neustále vybíjajú, takže pamäť treba neustále obnovovať. Dokonca aj chvíľkové prerušenie napájania alebo nejaký druh poruchy v obnovovacích cykloch vedie k strate náboja v bunke DRAM a následne k strate dát. V spustenom systéme to vedie k modrej obrazovke smrti, zlyhaniam globálnej bezpečnosti, poškodeniu súborov alebo úplnému zlyhaniu systému.

Typy RAM a výkon

Existujú určité nejasnosti týkajúce sa výkonu pamäte, pretože sa zvyčajne meria v nanosekundách, zatiaľ čo rýchlosť procesora sa meria v megahertzoch a gigahertzoch. Nové vysokorýchlostné pamäťové moduly sa merajú v megahertzoch, čo situáciu ešte viac komplikuje. Našťastie previesť jednu mernú jednotku na inú nie je ťažké.

Nanosekunda je jedna miliardtina sekundy, t.j. veľmi krátky časový úsek. Najmä rýchlosť svetla vo vákuu je 299 792 km/s, t.j. za jednu miliardtinu sekundy prejde svetelný lúč vzdialenosť rovnajúcu sa iba 29,98 cm, t.j. menšia ako dĺžka bežného pravítka.

Rýchlosť pamäťových čipov a systémov ako celku sa vyjadruje v megahertzoch (MHz), t.j. v miliónoch cyklov za sekundu alebo v gigahertzoch (GHz), t.j. v miliardách cyklov za sekundu. Moderné procesory majú takt medzi 2 a 4 GHz, hoci ich vnútorná architektúra (napr. viacjadrová) má oveľa väčší vplyv na ich výkon.

Keď sa frekvencia hodín zvyšuje, čas cyklu sa znižuje. V priebehu vývoja počítačov, aby sa zvýšila efektívnosť prístupu do pamäte, boli vytvorené rôzne úrovne cachovania na zachytenie prístupu procesora k pomalšej hlavnej pamäti. Len nedávno pamäťové moduly DDR, DDR2 a DDR3 SDRAM vyrovnali svoj výkon so zbernicou CPU. Keď sú frekvencie procesora a pamäťovej zbernice rovnaké, výkon pamäte sa stáva optimálnym pre konkrétny systém.

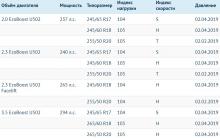

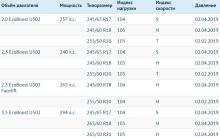

Do roku 2000 sa rýchlosť procesora a pamäťovej zbernice zvýšila na 100 a dokonca 133 MHz (tieto moduly sa nazývali PC100 a PC133). Začiatkom roku 2001 sa rýchlosť pamäte zdvojnásobila a dostala sa na 200 a 266 MHz; v roku 2002 boli vyrobené pamäťové moduly DDR s rýchlosťou 333 MHz a v roku 2003 - 400 a 533 MHz. V rokoch 2005 a 2006 nárast rýchlosti pamäte zodpovedal zvýšeniu rýchlosti procesorovej zbernice - zo 667 na 800 MHz. V roku 2007 bola rýchlosť pamätí DDR2 zvýšená na 1066 MHz a zároveň boli uvoľnené pamäte DDR3 s rovnakou a vyššou frekvenciou. V tabuľke nižšie sú uvedené hlavné typy pamäťových modulov a ich rýchlosť.

|

EDO. Extended Data Out (rozšírené možnosti výstupu dát).

DIMM. Dual Inline Memory Module (dual inline pamäťový modul).

DDR. Double Data Rate (dvojnásobná rýchlosť prenosu dát).

FPM. Režim rýchlej stránky (režim rýchlej stránky).

SIMM. Jeden inline pamäťový modul

RIMM. Rambus Inline Memory Module (štandardný pamäťový modul Rambus).

Výkon pamäte

Pri výmene chybného pamäťového modulu alebo čipu musí byť nový prvok rovnakého typu. Problémy sa zvyčajne vyskytujú pri použití čipov alebo modulov, ktoré nespĺňajú určité (nie príliš veľa) požiadaviek, ako je trvanie obnovovacích cyklov. Môžete sa tiež stretnúť s nesúladom pinov, kapacity, šírky bitov alebo dizajnu. Ak neviete, ktoré pamäťové moduly vaša základná doska umožňuje, pozrite si dokumentáciu.

Inštalácia rýchlejších pamäťových modulov vo všeobecnosti nezlepší výkon, pretože systém k nim pristupuje s rovnakou frekvenciou. V systémoch používajúcich moduly DIMM a RIMM sa rýchlosť a ďalšie charakteristiky časovania čítajú zo špeciálnej pamäte ROM SPD nainštalovanej na module. Pomocou týchto parametrov sa potom nakonfiguruje pamäťový radič. Výkon takýchto systémov možno zvýšiť inštaláciou rýchlejších pamäťových modulov až do limitu podporovaného čipovou sadou systémovej logiky.

Aby sa zdôraznili problémy s časovaním a spoľahlivosťou, Intel a JEDEC vytvorili štandardy pre vysokorýchlostné pamäťové moduly, ktoré definujú typy, ktoré spĺňajú určité úrovne výkonu. Podľa týchto noriem sú pamäťové moduly klasifikované podľa časových charakteristík.

Hlavnými príznakmi nedostatočného výkonu pamäte alebo jej nesúladu s charakteristikami časovania systému sú chyby pamäte a parity, ako aj „visiace“ a nestabilné fungovanie systému. V tomto prípade môže test POST tiež spôsobiť chyby. Ak si nie ste istý, ktoré pamäťové moduly sú pre váš systém prijateľné, obráťte sa na výrobcu počítača a pokúste sa zakúpiť pamäťové moduly od renomovaného dodávateľa.

Parity a kódy na opravu chýb (ECC)

Chyby pri ukladaní informácií do pamäte RAM sú nevyhnutné. Zvyčajne sa klasifikujú ako zlyhania hardvéru a občasné chyby (zlyhania).

Ak normálne fungujúci mikroobvod, napríklad v dôsledku fyzického poškodenia, začne pracovať nesprávne, potom sa to nazýva porucha hardvéru. Na vyriešenie tohto typu zlyhania je zvyčajne potrebné vymeniť niektorú časť pamäťového hardvéru, napríklad chybný čip, SIMM alebo DIMM.

Ďalším, zákernejším typom zlyhania je nepravidelná chyba (zrútenie). Ide o netrvalú poruchu, ktorá sa nevyskytuje pri opakovaných prevádzkových podmienkach alebo v pravidelných intervaloch. (Takéto poruchy sa zvyčajne „vyliečia“ vypnutím napájania počítača a jeho opätovným zapnutím.)

Približne pred 20 rokmi zamestnanci Intelu zistili, že príčinou porúch boli alfa častice. Keďže alfa častice nedokážu preniknúť ani do tenkého listu papiera, ukázalo sa, že pochádzajú z látky používanej v polovodičoch. Počas štúdie sa v plastových a keramických puzdrách mikroobvodov používaných v týchto rokoch našli častice tória a uránu. Zmenou výrobného procesu sa výrobcovia pamätí týchto nečistôt zbavili.

V súčasnosti výrobcovia pamätí takmer úplne eliminovali zdroje alfa častíc. V dôsledku toho mnohí výrobcovia pamäťových modulov odstránili paritu zo svojich produktov, aj keď zlyhania pamäte neboli úplne odstránené. Novšie výskumy ukázali, že častice alfa pokrývajú len malú časť príčin zlyhania pamäte.

Dnes je najväčšou príčinou nepravidelných chýb kozmické žiarenie. Keďže majú veľmi vysokú penetračnú schopnosť, chrániť sa pred nimi pomocou tienenia je takmer nemožné. Túto tézu potvrdilo množstvo štúdií uskutočnených spoločnosťou IBM pod vedením Dr. J.F. Ziegler.

Experiment na testovanie stupňa vplyvu kozmického žiarenia na výskyt chýb pri prevádzke mikroobvodov ukázal, že pomer signálu k chybe (pomer signálu k chybe - SER) pre niektoré moduly DRAM predstavoval 5950 jednotiek poruchovosti. (Failure Units - FU) za miliardu prevádzkových hodín pre každý mikroobvod. Merania sa uskutočňovali za podmienok blízkych skutočným, berúc do úvahy trvanie niekoľkých miliónov strojových hodín. Na priemernom počítači by to znamenalo chybu softvérovej pamäte približne každých šesť mesiacov. Na serverových systémoch alebo výkonných pracovných staniciach s množstvom nainštalovanej pamäte RAM tieto štatistiky poukazujú na jedno (alebo viac) zlyhanie pamäte každý mesiac! Keď bol testovací systém s rovnakými modulmi DIMM umiestnený v bezpečnom úkryte v hĺbke viac ako 15 metrov pod vrstvou horniny, ktorá úplne eliminuje vplyv kozmického žiarenia, nezaznamenali sa vôbec žiadne programátorské chyby v pamäti. Experiment preukázal nielen nebezpečenstvo vplyvu kozmického žiarenia, ale dokázal aj to, aké efektívne je eliminovať vplyv alfa žiarenia a rádioaktívnych nečistôt v obaloch pamäťových modulov.

Chyby kozmického žiarenia sú nebezpečnejšie pre moduly SRAM ako pre DRAM, pretože náboj potrebný na uloženie jedného bitu v bunke SRAM je oveľa menší ako kapacita kondenzátora DRAM. Kozmické žiarenie predstavuje veľké nebezpečenstvo aj pre pamäťové čipy s vysokou hustotou. Čím vyššia je hustota pamäťových buniek, tým vyššia je pravdepodobnosť, že kozmický lúč zasiahne takúto bunku. S rastúcim množstvom pamäte sa zvyšuje aj chybovosť.

Bohužiaľ, výrobcovia počítačov nerozpoznali toto ako príčinu chýb pamäte. Náhodná povaha zlyhania sa dá oveľa ľahšie ospravedlniť elektrostatickým výbojom, veľkým prepätím alebo chybným správaním softvéru (napríklad použitím novej verzie operačného systému alebo veľkého aplikačného programu). Štúdie ukázali, že v prípade systémov ECC je podiel softvérových chýb 30-krát väčší ako pri hardvérových. A to nie je prekvapujúce vzhľadom na škodlivé účinky kozmického žiarenia. Počet chýb závisí od počtu nainštalovaných pamäťových modulov a ich veľkosti. Softvérové chyby sa môžu vyskytovať raz za mesiac, niekoľkokrát za týždeň alebo aj častejšie.

Hoci je príčinou väčšiny chýb programovacej pamäte kozmické žiarenie a žiarenie, existujú aj iné faktory.

Prepätie alebo šum na linke. Príčinou môže byť chybný zdroj napájania alebo nástenná zásuvka.

Používanie pamäte s nesprávnym typom alebo charakteristikami. Typ pamäte musí byť podporovaný konkrétnou čipovou sadou a mať prístupovú rýchlosť definovanú touto sadou.

Statické výboje. Spôsobuje krátkodobé prepätia, ktoré môžu ovplyvniť integritu údajov.

Chyby synchronizácie. Údaje neprijaté včas môžu spôsobiť chyby softvéru. Príčinou sú často nesprávne nastavenia systému BIOS, RAM, ktorá je pomalšia, než vyžaduje systém, pretaktované procesory a ďalšie súčasti systému.

Odvod tepla. Vysokorýchlostné pamäťové moduly majú vyššie prevádzkové teploty ako staršie pamäťové moduly. Prvými modulmi vybavenými rozptyľovačmi tepla boli moduly RDRAM RIMM; teraz je veľa vysokovýkonných modulov DDR2 a DDR3 vybavených rozdeľovačmi tepla, pretože je to jediný spôsob, ako sa vysporiadať so zvýšenou úrovňou tvorby tepla.

Väčšina opísaných problémov nespôsobuje prerušenie činnosti pamäťových čipov (hoci zlé napájanie alebo statická elektrina ich môže fyzicky poškodiť), ale môžu ovplyvniť uložené dáta.

Ignorovanie zlyhaní samozrejme nie je najlepší spôsob, ako sa s nimi vysporiadať. Na zlepšenie odolnosti voči chybám v moderných počítačoch sa používajú techniky ako parita a kódy na opravu chýb (ECC).

Systémy bez parity vôbec neposkytujú odolnosť voči chybám. Jediným dôvodom ich použitia je ich minimálna základná cena. Zároveň na rozdiel od iných technológií nie je potrebná dodatočná pamäť RAM. Dátový bajt s paritou obsahuje 9 bitov namiesto 8 bitov, takže cena pamäte s paritou je asi o 12,5 % vyššia. Okrem toho majú radiče pamäte, ktoré nevyžadujú logické mosty na počítanie paritných alebo ECC údajov, zjednodušenú vnútornú architektúru. Prenosné systémy, pre ktoré je otázka minimálnej spotreby energie obzvlášť dôležitá, profitujú zo zníženého napájania pamätí vďaka použitiu menšieho počtu DRAM čipov. Napokon, neparitná pamäťová dátová zbernica má menšiu bitovú šírku, čo sa premieta do zníženia počtu dátových vyrovnávacích pamätí. Štatistická pravdepodobnosť chýb pamäte v moderných stolných počítačoch je približne jedna chyba každých niekoľko mesiacov. Počet chýb závisí od množstva a typu použitej pamäte.

Táto úroveň chýb môže byť prijateľná pre bežné počítače, ktoré sa nepoužívajú na kritické aplikácie. V tomto prípade hrá hlavnú úlohu cena a dodatočné náklady na pamäťové moduly s podporou parity a kód ECC sa neospravedlňujú, takže je ľahšie vyrovnať sa so zriedkavými chybami.

Parita

Ide o jeden zo štandardov predstavených IBM, podľa ktorého sú informácie v pamäťových bankách uložené vo fragmentoch po 9 bitoch, pričom osem z nich (tvoriacich jeden bajt) je určených pre samotné dáta a deviaty je paritný bit. Použitie deviateho bitu umožňuje schémam správy pamäte na úrovni hardvéru kontrolovať integritu každého bajtu údajov. Ak sa zistí chyba, počítač sa zastaví a na obrazovke sa zobrazí chybové hlásenie. Ak používate počítač so systémom Windows alebo OS/2, ak sa vyskytne chyba parity, správa sa nemusí zobraziť, ale systém sa jednoducho zablokuje. Po reštarte by mal systém BIOS identifikovať chybu a vydať príslušné hlásenie.

Moduly SIMM a DIMM sa dodávajú s podporou parity alebo bez nej.

Prvé počítače používali paritnú pamäť na nastavenie presnosti vykonávaných operácií. Počnúc rokom 1994 sa na trhu PC začal rozvíjať znepokojujúci trend. Väčšina spoločností začala ponúkať počítače bez paritnej pamäte a bez prostriedkov na detekciu alebo opravu chýb. Použitie modulov SIMM bez parity znížilo náklady na pamäť o 10-15%. Pamäť s paritou bola zase drahšia kvôli použitiu dodatočných paritných bitov. Technológia parity neopravuje systémové chyby, ale poskytuje používateľovi počítača možnosť ich odhaliť, čo má nasledujúce výhody:

kontrola parity chráni pred následkami nesprávnych výpočtov založených na nesprávnych údajoch;

Kontrola parity presne určí zdroj chýb, pomôže vám pochopiť problém a zlepší spoľahlivosť vášho počítača.

Implementácia podpory pamäte s paritou alebo bez nej vyžaduje len malé úsilie. Najmä nebude ťažké implementovať podporu parity pre základnú dosku. Hlavné náklady na implementáciu súvisia s nákladmi na samotné paritné pamäťové moduly. Ak sú zákazníci ochotní vynaložiť dodatočné náklady na zlepšenie spoľahlivosti systémov, ktoré si objednávajú, výrobcovia počítačov im môžu poskytnúť takúto príležitosť.

Schéma kontroly parity

Pri vývoji štandardu parity IBM určila, že hodnota paritného bitu je nastavená tak, že počet jednotiek vo všetkých deviatich bitoch (osem dátových bitov a paritný bit) je nepárny. Inými slovami, keď sa do pamäte zapíše bajt (8 bitov), špeciálny obvod kontroly parity (čip nainštalovaný na základnej doske alebo pamäťovej doske) spočíta počet jednotiek v byte. Ak je párny, na výstupe mikroobvodu sa generuje signál logickej jednotky, ktorý je uložený v príslušnom pamäťovom bite ako deviaty bit (paritný bit). Celkový počet jednotiek vo všetkých deviatich čísliciach sa stane nepárnym. Ak je počet jednotiek v ôsmich bitoch pôvodných dát nepárny, potom je paritný bit nula a súčet binárnych číslic v deviatich bitoch tiež zostáva nepárny.

Zvážte konkrétny príklad (pamätajte na to, že bity v byte sú číslované od nuly, t.j. 0, 1, 2, ..., 7).

Bitová hodnota: 1 0 1 1 0 0 1 1 0

V tomto prípade je celkový počet 1 dátových bitov nepárny (5), takže paritný bit musí byť nula.

Uvažujme ešte o jednom príklade.

Dátový bit: 0 1 2 3 4 5 6 7 paritný bit

Bitová hodnota: 0 0 1 1 0 0 1 1 1

V tomto príklade je celkový počet 1 dátových bitov párny (4), takže paritný bit musí byť 1, takže počet 1 vo všetkých deviatich bitoch je nepárny.

Pri čítaní z pamäte ten istý čip kontroluje paritu informácií. Ak je počet jednotiek v 9-bitovom byte párny, pri čítaní alebo zápise údajov sa vyskytla chyba. Nedá sa určiť, v akom výboji k nemu došlo (nedá sa zistiť ani počet poškodených výbojov). Okrem toho, ak k zlyhaniu došlo v troch bitoch (v nepárnom počte z nich), chyba bude opravená; dva chybné bity (alebo ich párny počet) však nezaznamenajú poruchu. Keďže súčasná chyba v niekoľkých bitoch jedného bajtu je extrémne nepravdepodobná, takáto overovacia schéma bola lacná a zároveň umožňovala s vysokou pravdepodobnosťou odhaliť chyby v pamäti.

Keď sa zistí chyba, paritný obvod na základnej doske vygeneruje nemaskovateľné prerušenie (NMI), systémové varovanie, ktoré programy nemôžu ignorovať. Hlavná práca sa zastaví a spustí sa špeciálny postup napísaný v systéme BIOS.

Ešte pred niekoľkými rokmi, keď bola pamäť drahá, niektoré spoločnosti vydávali SIMM s fiktívnymi paritnými čipmi. Namiesto ukladania paritných bitov pre každý bajt pamäte tieto čipy generovali vždy správny doplnkový bit. Keď sa teda systém pokúsil zapísať paritný bit, bol jednoducho vyradený a pri čítaní bajtu bol vždy nahradený „potrebným“ paritným bitom. Vďaka tomu systém vždy dostával informácie o správnom fungovaní pamäte, hoci v skutočnosti k nej mohlo byť všetko ďaleko.

Takéto podvodné aktivity boli spôsobené vysokou cenou pamäťových čipov a výrobcovia boli ochotní preplatiť pár dolárov navyše za generátor, aby neplatili za drahší čip, ktorý uchováva paritné bity. Bohužiaľ bolo pomerne ťažké určiť prítomnosť takéhoto generátora v pamäťovom module. Generátor falošnej parity sa navonok líšil od bežných pamäťových čipov a mal označenie odlišné od ostatných čipov modulu. Väčšina generátorov mala logo „GSM“, ktoré označovalo výrobcu logiky kontroly parity, často odlišnú od spoločnosti, ktorá vyrobila samotný pamäťový modul.

Hardvérové testery boli jediným nástrojom, ktorý dokázal odhaliť moduly s falošnou paritou. Teraz cena pamäte klesla, čo odstránilo hlavnú príčinu takéhoto podvodu.

Kód opravy chyby

Kódy na opravu chýb (ECC) umožňujú chybu nielen odhaliť, ale aj opraviť v jednom bite. Preto počítač, ktorý používa takéto kódy, v prípade chyby v jednom bite môže pracovať bez prerušenia a dáta sa nepoškodia. Kódy na opravu chýb vo väčšine počítačov zisťujú iba dvojbitové chyby, ale neopravujú ich. Zároveň je približne 98 % výpadkov pamäte spôsobených práve chybou v jednom bite, t.j. je úspešne opravený pomocou tohto typu kódov. Tento typ ECC sa nazýva SEC_DED (táto skratka znamená „jednobitová korekcia, dvojbitová detekcia chýb“).

V kódoch na opravu chýb tohto typu sa na každých 32 bitov vyžaduje ďalších sedem kontrolných bitov pre 4-bajtovú organizáciu a osem pre 8-bajtovú organizáciu (64-bitové procesory Athlon / Pentium). Implementácia kódu na opravu chýb so 4-bajtovou organizáciou je samozrejme drahšia ako bežná kontrola parity, ale pri 8-bajtovej organizácii sú ich náklady rovnaké, pretože vyžadujú rovnaký počet dodatočných bitov.

Na použitie kódov na opravu chýb je potrebný pamäťový radič, ktorý vypočítava kontrolné bity počas operácie zápisu do pamäte. Pri čítaní z pamäte takýto ovládač porovnáva načítané a vypočítané hodnoty riadiacich bitov a v prípade potreby opravuje poškodený bit (alebo bity). Náklady na dodatočnú logiku na implementáciu kódu opravy chýb v pamäťovom radiči nie sú príliš vysoké, ale môžu výrazne znížiť výkon pamäte počas operácií zápisu. Je to preto, že operácie zápisu a čítania musia čakať na dokončenie kontrolných bitov. Pri písaní časti slova by ste si mali najskôr prečítať celé slovo, potom prepísať zmenené bajty a až potom - nové vypočítané kontrolné bity.

Vo väčšine prípadov dôjde k zlyhaniu pamäte v jednom bite, a preto sú takéto chyby úspešne opravené pomocou kódu na opravu chýb. Použitie pamäte odolnej voči chybám zaisťuje vysokú spoľahlivosť počítača. Pamäť ECC je určená pre servery, pracovné stanice alebo aplikácie, kde potenciálne náklady na chybu výpočtu výrazne prevyšujú dodatočné investície do hardvéru a systémového času. Ak sú údaje mimoriadne dôležité a na riešenie dôležitých úloh sa používajú počítače, pamäť ECC je nevyhnutná. V skutočnosti žiadny systémový inžinier, ktorý rešpektuje seba, nepoužije server, ani ten najnenáročnejší, bez pamäte ECC.

Používatelia majú na výber medzi neparitnými, paritnými a ECC systémami, t.j. medzi požadovanou úrovňou odolnosti počítača voči chybám a stupňom hodnoty použitých údajov.

Záver

Na použitie kódov na opravu chýb je potrebný pamäťový radič, ktorý vypočítava kontrolné bity počas operácie zápisu do pamäte. Náklady na dodatočnú logiku na implementáciu kódu opravy chýb v pamäťovom radiči nie sú príliš vysoké, ale môžu výrazne znížiť výkon pamäte počas operácií zápisu. Je to preto, že operácie zápisu a čítania musia čakať na dokončenie kontrolných bitov.

Použitie pamäte odolnej voči chybám zaisťuje vysokú spoľahlivosť počítača. Pamäť ECC je určená pre servery, pracovné stanice alebo aplikácie, kde potenciálne náklady na chybu výpočtu výrazne prevyšujú dodatočné investície do hardvéru a systémového času. Ak sú údaje mimoriadne dôležité a na riešenie dôležitých úloh sa používajú počítače, pamäť ECC je nevyhnutná.

V počítači je oveľa dynamickejšia pamäť ako statická pamäť, pretože je to DRAM, ktorá sa používa ako hlavná pamäť VM. Podobne ako SRAM, aj dynamická pamäť pozostáva z jadra (ZE pole) a logiky rozhrania (bufferové registre, zosilňovače na čítanie dát, regeneračné obvody atď.). Hoci počet typov DRAM už presiahol dve desiatky, ich jadro je organizované takmer rovnako. Hlavné rozdiely súvisia s logikou rozhrania a tieto rozdiely sú spôsobené aj rozsahom mikroobvodov - okrem hlavnej pamäte VM sú integrované obvody dynamickej pamäte zahrnuté napríklad vo video adaptéroch. Klasifikácia dynamických pamäťových čipov je znázornená na obr. 72.

Aby sme pochopili rozdiely medzi typmi DRAM, pozrime sa najprv na algoritmus pre prácu s dynamickou pamäťou. Na to použijeme Obr. 68.

Na rozdiel od SRAM sa adresa bunky DRAM prenáša na čip v dvoch krokoch - najprv adresa stĺpca a potom riadok, čo umožňuje znížiť počet pinov adresovej zbernice približne na polovicu, zmenšiť veľkosť balenia a umiestniť viac čipy na základnej doske. To samozrejme vedie k pomalšiemu výkonu, pretože prenos adresy trvá dvakrát dlhšie. Na označenie, ktorá časť adresy je v určitom okamihu prenášaná, slúžia dva pomocné signály RAS a CAS. Pri prístupe k pamäťovej bunke sa adresa reťazca nastaví na adresovú zbernicu. Po stabilizácii procesov na zbernici je daný signál RAS a adresa je zapísaná do vnútorného registra pamäťového čipu. Adresa stĺpca sa potom nastaví na adresovej zbernici a vydá sa signál CAS. V závislosti od stavu linky WE sa dáta čítajú z bunky alebo zapisujú do bunky (pred zápisom je potrebné dáta umiestniť na dátovú zbernicu). Interval medzi nastavením adresy a vydaním signálu RAS (alebo CAS) je určený technickými charakteristikami mikroobvodu, ale zvyčajne sa adresa nastavuje v jednom cykle systémovej zbernice a riadiaci signál v ďalšom. Na čítanie alebo zápis jednej bunky DRAM je teda potrebných päť cyklov, v ktorých nastane nasledovné: vydanie adresy riadka, vydanie signálu RAS, vydanie adresy stĺpca, vydanie signálu CAS, vykonanie operácie čítania/zápisu (v statickej pamäti postup trvá len dva až tri ťahy).

Ryža. 72. Klasifikácia dynamickej RAM: a) - čipy pre hlavnú pamäť; b) - čipy pre video adaptéry.

Mali by ste si tiež uvedomiť potrebu regenerácie údajov. Ale spolu s prirodzeným vybitím kondenzátora GE v priebehu času vedie čítanie údajov z DRAM aj k strate náboja, takže po každej operácii čítania je potrebné údaje obnoviť. To sa dosiahne prepísaním rovnakých údajov ihneď po prečítaní. Pri čítaní informácií z jednej bunky sa v skutočnosti naraz rozdajú údaje z celého vybraného riadku, ale použijú sa iba tie, ktoré sú v stĺpci záujmu, a všetky ostatné sa ignorujú. Operácia čítania z jednej bunky teda vedie k zničeniu údajov celého riadku a je potrebné ich obnoviť. Regenerácia dát po načítaní prebieha automaticky logikou rozhrania čipu a deje sa tak ihneď po načítaní riadku.

Teraz sa pozrime na rôzne typy dynamických pamäťových čipov, počnúc systémovými DRAM, teda čipmi určenými na použitie ako hlavná pamäť. V počiatočnom štádiu to boli asynchrónne pamäťové mikroobvody, ktorých činnosť nebola pevne viazaná na hodinové impulzy systémovej zbernice.

Asynchrónna dynamická RAM. Asynchrónne dynamické čipy RAM sú riadené signálmi RAS a CAS a ich činnosť v zásade priamo nesúvisí s hodinami zbernice. Asynchrónna pamäť sa vyznačuje dodatočným časom stráveným interakciou pamäťových čipov a radiča. Takže v asynchrónnom obvode bude signál RAS generovaný až po príchode hodinového impulzu do ovládača a po určitom čase bude vnímaný pamäťovým čipom. Potom pamäť vydá údaje, ale ovládač ich bude môcť prečítať až po príchode ďalšieho hodinového impulzu, pretože musí pracovať synchrónne so zvyškom zariadení VM. Počas cyklu čítania/zápisu teda dochádza k malým oneskoreniam v dôsledku čakania pamäte radiča a pamäťového radiča.

DRAM čipy. Prvé dynamické pamäťové čipy využívali najjednoduchší spôsob výmeny dát, často nazývaný tradičný. Umožňoval čítať a zapisovať pamäťový riadok iba v každom piatom cykle. . Kroky tohto postupu boli opísané vyššie. Tradičná DRAM zodpovedá vzorcu 5-5-5-5. Čipy tohto typu mohli pracovať na frekvenciách do 40 MHz a pre svoju pomalosť (prístupová doba bola cca 120 ns) dlho nevydržali.

čipy FPMDRAM.Čipy DRAM, ktoré implementujú režim FPM, sú tiež prvými typmi DRAM. Podstata režimu sa ukázala skôr. Schéma čítania pre FPM DRAM je opísaná vzorcom 5-3-3-3 (celkovo 14 cyklov). Použitie schémy rýchleho stránkovania znížilo prístupový čas na 60 ns, čo pri zohľadnení schopnosti pracovať na vyšších frekvenciách zbernice viedlo k zvýšeniu výkonu pamäte približne o 70 % v porovnaní s tradičnou DRAM. Tento typ mikročipu sa používal v osobných počítačoch približne do roku 1994.

Čipy EDO DRAM.Ďalším krokom vo vývoji dynamickej pamäte RAM boli integrované obvody s režim prístupu k hyperstránke(HPM, Hyper Page Mode), známejšie ako EDO (Extended Data Output – predĺžený čas uchovávania dát na výstupe). Hlavnou črtou technológie je dlhší čas dostupnosti dát na výstupe čipu v porovnaní s FPM DRAM. V čipoch FPM DRAM zostávajú výstupné dáta platné iba vtedy, keď je aktívny signál CAS, a preto druhý a ďalší prístup k linke vyžaduje tri cykly: cyklus prepínania CAS do aktívneho stavu, cyklus čítania dát a CAS prepnúť cyklus do neaktívneho stavu. V EDO DRAM sa na aktívnej (zostupnej) hrane signálu CAS dáta uložia do interného registra, kde sa uložia ešte nejaký čas po príchode ďalšej aktívnej hrany signálu. To umožňuje použitie uložených údajov, keď je CAS už neaktívny. Inými slovami, časové parametre sa zlepšujú vďaka eliminácii čakacích cyklov na moment stabilizácie dát na výstupe mikroobvodu.

Čítacia schéma EDO DRAM je už 5-2-2-2, čo je o 20 % rýchlejšie ako FPM. Čas prístupu je asi 30-40 ns. Je potrebné poznamenať, že maximálna frekvencia systémovej zbernice pre čipy EDO DRAM by nemala presiahnuť 66 MHz.

Čipsy BEDO DRAM. Technológia EDO bola vylepšená spoločnosťou VIA Technologies. Nová modifikácia EDO je známa ako BEDO (Burst EDO - dávkové EDO). Novinkou metódy je, že pri prvom prístupe sa načíta celý riadok mikroobvodu, ktorý obsahuje po sebe idúce slová paketu. Sekvenčný prenos slov (prepínanie stĺpcov) je automaticky monitorovaný vnútorným počítadlom mikroobvodu. To eliminuje potrebu vydávať adresy pre všetky bunky v pakete, ale vyžaduje si podporu externej logiky. Metóda umožňuje skrátiť čas čítania druhého a nasledujúcich slov o ďalší cyklus, vďaka čomu má vzorec tvar 5-1-1-1.

EDRAM čipy. Rýchlejšiu verziu DRAM vyvinula Enhanced Memory Systems, divízia Ramtronu. Technológia je implementovaná vo variantoch FPM, EDO a BEDO. Čip má rýchlejšie jadro a vnútornú vyrovnávaciu pamäť. Prítomnosť druhého je hlavnou črtou technológie. Cache pamäť je statická pamäť (SRAM) s kapacitou 2048 bitov. Jadro EDRAM má 2048 stĺpcov, z ktorých každý je pripojený k vnútornej vyrovnávacej pamäti. Pri prístupe k ľubovoľnej bunke sa súčasne načíta celý riadok (2048 bitov). Čítací riadok sa vkladá do SRAM a prenos informácií do vyrovnávacej pamäte nemá prakticky žiadny vplyv na výkon, pretože prebieha v jednom hodinovom cykle. Pri ďalších prístupoch k bunkám patriacim do rovnakého riadku sa údaje preberajú z rýchlejšej vyrovnávacej pamäte. K ďalšiemu volaniu do jadra dôjde pri prístupe k bunke, ktorá sa nenachádza v riadku uloženom vo vyrovnávacej pamäti mikroobvodu.

Táto technológia je najúčinnejšia pre sekvenčné čítanie, to znamená, keď sa priemerný čas prístupu pre mikroobvod blíži k hodnotám typickým pre statickú pamäť (asi 10 ns). Hlavný problém spočíva v nekompatibilite s ovládačmi používanými pri práci s inými typmi DRAM.

Synchrónna dynamická RAM. V synchrónnych DRAM je výmena informácií synchronizovaná externými hodinovými signálmi a prebieha v presne definovaných časových bodoch, čo umožňuje plne využiť šírku pásma zbernice procesor-pamäť a vyhnúť sa čakacím cyklom. Adresa a riadiace informácie sú zaznamenané v pamäťovom IC. Potom nastane odozva mikroobvodu po dobre definovanom počte hodinových impulzov a procesor môže tento čas využiť na iné akcie, ktoré nesúvisia s prístupom do pamäte. Pri synchrónnej dynamickej pamäti namiesto trvania prístupového cyklu hovoria o minimálnej prípustnej perióde taktovacej frekvencie a to už hovoríme o čase rádovo 8-10 ns.

čipy SDRAM. Skratka SDRAM (Synchronous DRAM – synchrónna DRAM) sa používa na označenie čipov „normálnej“ synchrónnej dynamickej RAM. Základné rozdiely medzi SDRAM a asynchrónnou dynamickou RAM diskutovanou vyššie možno zredukovať na štyri body:

synchrónny spôsob prenosu dát na zbernicu;

dopravníkový mechanizmus na odoslanie paketu;

Použitie niekoľkých (dvoch alebo štyroch) vnútorných pamäťových bánk;

Prenos časti funkcií pamäťového radiča na logiku samotného mikroobvodu.

Synchronizácia pamäte umožňuje pamäťovému radiču „vedieť“, kedy sú dáta pripravené, čím sa znižuje réžia čakania a hľadania dát. Keďže dáta sa objavujú na výstupe IC súčasne s hodinovými impulzmi, interakcia pamäte s inými VM zariadeniami je zjednodušená.

Na rozdiel od BEDO, pipeline umožňuje, aby paketové dáta prechádzali hodinami, takže RAM môže fungovať hladko pri vyšších frekvenciách ako asynchrónna RAM. Výhody pipeline sa zvyšujú najmä pri prenose dlhých paketov, ktoré však nepresahujú dĺžku čipovej linky.

Významný účinok sa dosiahne rozdelením celej sady buniek do nezávislých vnútorných polí (banky). To umožňuje spojiť prístup do bunky jednej banky s prípravou na ďalšiu operáciu v iných bankách (dobíjanie riadiacich obvodov a obnova informácií). Schopnosť ponechať otvorených niekoľko riadkov pamäte súčasne (z rôznych bánk) tiež zlepšuje výkon pamäte. Pri sekvenčnom prístupe k bankám frekvencia prístupu ku každej z nich individuálne klesá úmerne počtu bánk a SDRAM môže pracovať na vyšších frekvenciách. Vďaka vstavanému čítaču adries umožňuje SDRAM, podobne ako BEDO DRAM, čítanie a zápis v burst režime a v SDRAM sa mení dĺžka paketu a v burst režime je možné prečítať celý pamäťový riadok. IC možno charakterizovať vzorcom 5-1-1-1. Hoci vzorec pre tento typ dynamickej pamäte je rovnaký ako pri BEDO, schopnosť pracovať na vyšších frekvenciách znamená, že dvojbanková SDRAM pri rýchlosti zbernice 100 MHz môže takmer zdvojnásobiť výkon pamäte typu BEDO.

Čipy DDR SDRAM. Dôležitým krokom v ďalšom vývoji technológie SDRAM bola DDR SDRAM (Double Data Rate SDRAM – SDRAM s dvojnásobnou rýchlosťou prenosu dát). Na rozdiel od SDRAM nová modifikácia dodáva dáta v burst móde na oboch hranách synchronizačného impulzu, vďaka čomu je priepustnosť dvojnásobná. Existuje niekoľko špecifikácií DDR SDRAM v závislosti od taktovacej frekvencie systémovej zbernice: DDR266, DDR333, DDR400, DDR533. Špičková šírka pásma pamäťového čipu DDR333 je teda 2,7 GB/s a pre DDR400 je to 3,2 GB/s. DDR SDRAM je v súčasnosti najbežnejším typom dynamickej pamäte v osobných VM.

Čipy RDRAM, DRDRAM. Najzrejmejším spôsobom, ako zvýšiť efektivitu procesora s pamäťou, je zvýšiť frekvenciu hodín zbernice alebo šírku vzorky (počet bitov odoslaných súčasne). Bohužiaľ, pokusy o kombináciu oboch možností narážajú na značné technické ťažkosti (so zvýšením frekvencie sa problémy s elektromagnetickou kompatibilitou zhoršujú, je ťažšie zabezpečiť súčasný príjem všetkých bitov informácií prenášaných paralelne k spotrebiteľovi). Väčšina synchrónnych DRAM (SDRAM, DDR) používa široké vzorkovanie (64 bitov) s obmedzenou frekvenciou zbernice.

Zásadne odlišný prístup k budovaniu DRAM navrhol Rambus v roku 1997. Zameriava sa na zvýšenie taktovacej frekvencie na 400 MHz pri súčasnom znížení šírky vzorky na 16 bitov. Nová pamäť je známa ako RDRAM (Rambus Direct RAM). Existuje niekoľko druhov tejto technológie: Base, Concurrent a Direct. Celkovo sa taktovanie vykonáva na oboch okrajoch hodinových signálov (ako v DDR), vďaka čomu je výsledná frekvencia 500-600, 600-700 a 800 MHz. Prvé dve možnosti sú takmer totožné, no zmeny v technológii Direct Rambus (DRDRAM) sú dosť výrazné.

Najprv sa zastavme pri základných aspektoch technológie RDRAM, pričom sa zameriame hlavne na modernejšiu verziu – DRDRAM. Hlavným rozdielom od ostatných typov DRAM je originálny systém výmeny dát medzi jadrom a pamäťovým radičom, ktorý je založený na takzvanom „Rambus channel“, ktorý využíva asynchrónny blokovo orientovaný protokol. Na logickej úrovni sa informácie medzi radičom a pamäťou prenášajú v paketoch.

Existujú tri typy paketov: dátové pakety, riadkové pakety a stĺpcové pakety. Pakety riadkov a stĺpcov slúžia na prenos príkazov z pamäťového radiča na ovládanie riadkov riadkov a stĺpcov poľa pamäťových prvkov, resp. Tieto inštrukcie nahrádzajú konvenčný čipový riadiaci systém signálmi RAS, CAS, WE a CS.

Pole GE je rozdelené do bánk. Ich počet v kryštáli s kapacitou 64 Mbit je 8 nezávislých alebo 16 duálnych bánk. V duálnych bankách má pár bánk spoločné zosilňovače na čítanie/zápis. Vnútorné jadro mikroobvodu má 128-bitovú dátovú zbernicu, ktorá umožňuje preniesť 16 bajtov na každú adresu stĺpca. Pri zápise môžete použiť masku, v ktorej každý bit zodpovedá jednému bajtu paketu. Pomocou masky môžete určiť, koľko bajtov paketu a ktoré sa majú zapísať do pamäte.

Dátové, riadkové a stĺpcové riadky v kanáli sú úplne nezávislé, takže riadkové príkazy, stĺpcové príkazy a dáta možno prenášať súčasne a pre rôzne čipové banky. Stĺpcové pakety obsahujú dve polia a sú prenášané cez päť riadkov. Prvé pole určuje hlavnú operáciu zápisu alebo čítania. Druhé pole obsahuje buď označenie použitia masky záznamu (samotná maska sa prenáša po dátových linkách), alebo rozšírený operačný kód, ktorý určuje variant pre hlavnú operáciu. Pakety riadkov sú rozdelené na príkazy aktivácie, zrušenia, obnovenia a vypínača. Na prenos linkových paketov sú pridelené tri linky.

Operácia zápisu môže bezprostredne nasledovať po čítaní - všetko, čo je potrebné, je oneskorenie po dobu prechodu signálu kanálom (od 2,5 do 30 ns, v závislosti od dĺžky kanála). Pre vyrovnanie oneskorení pri prenose jednotlivých bitov prenášaného kódu musia byť vodiče na doske striktne rovnobežné, musia mať rovnakú dĺžku (dĺžka čiar by nemala presiahnuť 12 cm) a spĺňať prísne požiadavky určené vývojárom. .

Každý zápis v kanáli môže byť zreťazený, pričom oneskorenie prvého dátového paketu je 50 ns a zvyšok operácií čítania/zápisu sa vykonáva nepretržite (oneskorenie sa zavedie iba vtedy, keď sa operácia zmení zo zápisu na čítanie a naopak naopak).

Dostupné publikácie uvádzajú prácu spoločností Intel a Rambus na novej verzii RDRAM s názvom nDRAM, ktorá bude podporovať prenosové rýchlosti až do 1600 MHz.

SLDRAM čipy. Potenciálnym konkurentom RDRAM pre úlohu štandardu architektúry pamäte pre budúce osobné VM je nový typ dynamickej RAM, vyvinutý konzorciom výrobcov VM SyncLink Consortium a známy pod skratkou SLDRAM. Na rozdiel od RDRAM, ktorej technológia je majetkom spoločností Rambus a Intel, je tento štandard otvorený. Na systémovej úrovni sú technológie veľmi podobné. Dáta a príkazy z ovládača do pamäte a späť do SLDRAM sa prenášajú v paketoch po 4 alebo 8 balíkoch. Príkazy, adresy a riadiace signály sa odosielajú cez jednosmernú 10-bitovú príkazovú zbernicu. Dáta na čítanie a zápis sa prenášajú cez obojsmernú 18-bitovú dátovú zbernicu. Oba autobusy premávajú na rovnakej frekvencii. Táto frekvencia je zatiaľ stále 200 MHz, čo je vďaka technológii DDR ekvivalent 400 MHz. Ďalšie generácie SLDRAM by mali pracovať na frekvencii 400 MHz a vyššej, teda poskytovať efektívnu frekvenciu vyššiu ako 800 MHz.

K jednému ovládaču je možné pripojiť až 8 pamäťových čipov. Aby sa predišlo oneskoreniu signálu z mikroobvodov, ktoré sú od ovládača vzdialenejšie, určujú sa charakteristiky časovania pre každý mikroobvod a zadávajú sa do jeho riadiaceho registra pri zapnutí napájania.

ESDRAM čipy. Toto je synchrónna verzia EDRAM, ktorá využíva rovnaké techniky redukcie prístupového času. Operácia zápisu, na rozdiel od čítania, obchádza vyrovnávaciu pamäť, čo zlepšuje výkon ESDRAM pri obnovení čítania z riadku, ktorý sa už nachádza vo vyrovnávacej pamäti. Vďaka prítomnosti dvoch bánk v čipe sú minimalizované prestoje kvôli príprave na operácie čítania/zápisu. Nevýhody uvažovaného mikroobvodu sú rovnaké ako nevýhody EDRAM - komplikácia ovládača, pretože musí čítať možnosť prípravy na čítanie nového riadku jadra do vyrovnávacej pamäte. Navyše, pri ľubovoľnom poradí adries sa vyrovnávacia pamäť využíva neefektívne.

CDRAM čipy. Tento typ pamäte RAM bol vyvinutý spoločnosťou Mitsubishi Corporation a možno ju považovať za revidovanú verziu ESDRAM bez niektorých jej nedokonalostí. Zmenila sa kapacita vyrovnávacej pamäte a princíp umiestňovania údajov do nej. Kapacita jedného bloku vyrovnávacej pamäte bola znížená na 128 bitov, takže 16-kilobitová vyrovnávacia pamäť môže súčasne ukladať kópie 128 pamäťových miest, čo umožňuje efektívnejšie využitie vyrovnávacej pamäte. Výmena prvej oblasti pamäte cache sa začne až po zaplnení posledného (128.) bloku. Zmenili sa aj spôsoby prístupu. Mikroobvod teda používa samostatné adresové zbernice pre statickú vyrovnávaciu pamäť a dynamické jadro. Prenos dát z dynamického jadra do vyrovnávacej pamäte je kombinovaný s vydávaním dát na zbernicu, takže časté, ale krátke prenosy neznižujú výkon IC pri čítaní veľkého množstva informácií z pamäte a vyrovnávajú CDRAM s ESDRAM , a pri čítaní na selektívnych adresách jednoznačne víťazí CDRAM. Treba však poznamenať, že vyššie uvedené zmeny viedli k ešte väčšej komplikácii pamäťového radiča.

Koniec práce -

Táto téma patrí:

Organizácia počítačov a systémov

Sibírska štátna letecká univerzita.. pomenovaná podľa akademika mf. Reshetneva.. organizácia počítačov a systémov..

Ak potrebujete ďalší materiál k tejto téme, alebo ste nenašli to, čo ste hľadali, odporúčame použiť vyhľadávanie v našej databáze diel:

Čo urobíme s prijatým materiálom:

Ak sa tento materiál ukázal byť pre vás užitočný, môžete si ho uložiť na svoju stránku v sociálnych sieťach:

| pípanie |

Všetky témy v tejto sekcii:

Úrovne detailov štruktúry počítača

Počítač ako kompletný objekt je ovocím úsilia špecialistov v rôznych oblastiach ľudského poznania. Každý špecialista považuje výpočtovú ma

Evolúcia výpočtovej automatizácie

Pokusy uľahčiť a v ideálnom prípade automatizovať proces výpočtovej techniky majú dlhú históriu siahajúcu viac ako 5000 rokov do minulosti. S rozvojom vedy a techniky sa nástroje automatizácie výpočtovej techniky neustále zvyšujú

Generácia nula (1492-1945)

Aby bol obraz úplný, spomenieme dve udalosti, ktoré nastali pred naším letopočtom: prvé počítadlo – počítadlo, vynájdené v starovekom Babylone v roku 3000 pred Kristom. e., a ich „modernejšia“ verzia s k

Prvá generácia (1937-1953)

Niekoľko vývojov si vyžiadalo úlohu prvého elektronického počítača v histórii v rôznych obdobiach. Spoločné mali použitie obvodov na báze vákuových elektrónok

Druhá generácia (1954-1962)

Druhá generácia sa vyznačuje množstvom úspechov v základni prvkov, štruktúre a softvéri. Všeobecne sa uznáva, že techno

Tretia generácia (1963-1972)

Tretia generácia bola poznačená dramatickým nárastom výpočtového výkonu VM, ktorý bol výsledkom veľkého pokroku v architektúre, technológii a softvéri. Osno

Štvrtá generácia (1972-1984)

Štvrtá generácia sa zvyčajne počíta od prechodu na integrované obvody veľkého (veľká integrácia, LSI) a extra veľké (veľmi rozsiahla integrácia, VLSI) stupňa a

Piata generácia (1984-1990)

Hlavným dôvodom oddelenia výpočtových systémov druhej polovice 80. rokov do samostatnej generácie bol rýchly vývoj CS so stovkami procesorov, ktorý sa stal impulzom

Koncept stroja s uloženým programom

Na základe cieľov tejto časti zavádzame novú definíciu pojmu „počítač“ ako súboru technických prostriedkov používaných na automatizované spracovanie diskrétnych

Princíp binárneho kódovania

Podľa tohto princípu sú všetky informácie, údaje aj príkazy, kódované binárnymi číslicami 0 a 1. Každý typ informácie je reprezentovaný binárnou postupnosťou a má svoju vlastnú

Princíp riadenia programu

Všetky výpočty, ktoré poskytuje algoritmus na riešenie problému, musia byť prezentované vo forme programu pozostávajúceho zo sekvencie riadiacich slov - príkazov. Každý tím predtým

Princíp homogenity pamäte

Príkazy a dáta sú uložené v rovnakej pamäti a sú v pamäti externe nerozoznateľné. Možno ich rozpoznať iba podľa spôsobu použitia. To vám umožní vykonávať príkazy rovnako

Architektúra von Neumanna

Von Neumannov článok definuje hlavné zariadenia VM, pomocou ktorých by sa vyššie uvedené princípy mali implementovať. Väčšina moderných VM svojou štruktúrou zodpovedá princípu softvéru.

Štruktúry počítačov

V súčasnosti získali dva spôsoby konštrukcie počítačov približne rovnakú distribúciu: s priamym pripojením a na báze zbernice. Predstavte si typický

Štruktúry výpočtových systémov